ijmemik

Volume 2 Issue 4 | December 2014

International Journal of Modern Engineering & Management Research Website: www.ijmemr.org

# Low Power Two-Stage Operational Amplifier design using 45 nm Technology

**Navneet Dubey**

Research Scholar ITM University, Gwalior (M.P.) [INDIA] Email: navneet.dubey8@gmail.com Dr. Shyam Akashe

Professor Department of Electronics and Communication Engg. ITM University Gwalior (M.P.) [INDIA] Email: shyam.akashe@itmuniversity.ac.in

# **1. INTRODUCTION**

Abstract—For low power Circuit work at the low voltage supply, but at low voltage supply voltage integrated circuitry design start to face a power wall as the most difficult constrains. In new technology and large demand in market of portable electronics equipment are increasing the interest in very low power integrated circuits. Designing very low power integrated circuit requires the reduction of the internal power supply voltages and interconnection parasitic element should be at least less and as these are the most important parameters that had been associated to power dissipation at certain supply to maintain the circuit performance at low voltage supply reduced the threshold voltage of the transistor which impose a large number of serious problem caused in both in circuit design and applied technology and techniques. After decreasing the threshold voltage the margin for error problems decrease and operational amplifier circuit parameter dramatically degrade the performance of original circuit in this paper we used current thus compensation technique to minimize the certain power consumption of low power amplifiers.

*Keywords:*—AC analysis, DC analysis, Transient analysis gain, Power dissipation, Cadence.

Operational amplifier, which has become new of the most versatile and important building blocks in analog circuit design. There are two operational amplifier developed. Operational Trans conductance amplifiers (unbuffered) have the output resistance typically very high. The other one is the buffered amplifier (voltage operational amplifier) typically low output resistance. Operational amplifier (control source) that have high forward gain so that when negative feedback is applied, the closed loop transfer function is practically independent of the gain of operational amplifier. This principal has been exploited to develop many useful analog circuit and system. The primary requirement of an operational amplifier is to have an open loop gain that is sufficiently large to implement the negative feedback concept. Here we use current compensation technique to minimize the power consumption here we design the operational amplifier using cadence 180nm technology and 65nm technology and calculate the gain and power consumption.

There are many factors that are diving the need to have lower power supply voltages in CMOS integrated circuits. As the channel length of CMOS technology decrease, the maximum allowable voltage will decrease. Also, as more components are include in the same area on integrated circuit, the power dissipation increase. Finally, the requirement for portable electronics implies battery operation which favour low voltage and low power circuits. These factors and other have caused many to suggest that future implementation of mixed analog digital circuit using standard CMOS will have power supplies more than 1v or less an important factor concerning analog circuits is that threshold voltage of future standard

CMOS technologies are not anticipated to decrease much below what is available today. It is necessary that the analog power supply be at least equal to the sum of the magnitude of the n-channel and p-channel threshold. This implies that low voltages analog circuits are in compatible with the CMOS technology trends of the future. Ways to circumvent this conflict are to develop technologies with lower threshold, increase the lower voltage power supply by on-chip dc-dc converter, or develop circuit techniques that are compatible with future standard CMOS technology trends.

The basic operational amplifier consists of four main blocks which as follows:

- A. Dual input Differential output.

- B. Differential input single ended output.

- C. Level shifter.

- D. Output buffer.

Complementary metal oxide semiconductor operational amplifier is very similar in architecture to their bipolar counter parts and also having an improvement in processing had been pushed scaling of device dimension persistently over the past many years. The main drive behind this trend is the resulting reduction in production cost since more components on a chip are possible. In addition to device scaling, the increase in the portable electronics market is also encouraging low voltage and low power circuitry since this would reduce battery size and weight and enable longer battery life time.

The third approach, developing analog circuit's techniques that compatible with future CMOS technology. There are many important advantage of certain approach thus; firstly, the need to develop expensive CMOS technology with less threshold voltages is avoided than Secondly, the high efficiency dc to dc converters are not even required. Thirdly, circuit techniques that permit low voltages operation with large threshold offer the for more fully utilizing potential the technology at higher voltages and at lower voltages if, might also be an fact the low threshold technologies do become standard technologies to be in use.

# 2. OP-AMP PRACTICAL CONSIDERATIONS

# 2. 1. Input/Output Offset Voltage

Op-amps do not always perform practically as they should theoretically. For example, sometimes an output voltage exists when both inputs are grounded. This output voltage is called output offset voltage and it is caused by an input offset voltage. If one is known the other can be calculated,

Vio

$$= V_{oo} / A_v$$

Imperfect transistors contained in the differential amplifier are responsible for the input offset voltage, which is usually no more than 2mV. The offset null pins on the IC opamp can be used with a potentiometer to take care of Vio and Voo.

# 2. 2. Input Bias Current / Input Offset Current

Similar to the offset voltages, there are currents flowing in or out of the inputs, and their average is known as input bias current, which may have a value of 80nA+. The currents on each input are not always equal and the difference between them is the input offset current. This is important because if the input bias currents are different, then the output voltage can be affected. So to keep the currents the same, each input needs to see the same resistance to ground, since identical currents will flow through identical resistances.

## 2. 3. Common Mode Rejection Ratio (CMRR)

The common mode rejection ratio (CMRR) is a ratio of the normal high gain that amplifies the difference of the signals on the inputs to the undesirable gain that amplifies a value when the signals are the same

## CMRR = Adiff/Acm

If op-amps were perfect, then there would be zero amplification when the same signal, or common-mode signal, feeds each input. The common-mode signal may be noise, so obviously it is not a good thing to amplify this noise. An acceptable CMRR is in the 90's (dB), where

CMRR = 20 log (Adiff/Acm) {in decibels (dB)}

# 2. 4. Output Short-Circuit Current

Op-amps do not output unlimited current because too much current flow could be damaging to the op-amp, particularly if a short circuit develops. Op-amps are made this way on purpose. An output short-circuit current of 25mA is a common value for an op amp. It follows that a low resistance load does not drop the expected voltage.

## **3. IMPLEMENTATION**

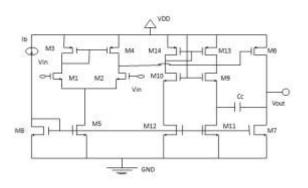

Here we implemented the operational amplifier using current compensation technique in cadence technology. Figure shows below the schematics diagram of operational amplifier.

#### Figure 3 schematic diagram of op-amp

Figure shows below the schematic diagram of operation amplifier. Here we implemented the operational amplifier. In the following figure we use NMOS and PMOS transistor and with a capacitor  $c_c$  thus NMOS transistor consist of following transistors as M1, M2, M5, M8, M7, M9, M10, M11 and M12 and also PMOS transistors consist of M3, M4, M6, M13 and M14 to demonstrate feasibility of the proposed low power operational amplifier circuit.

## Simulation:

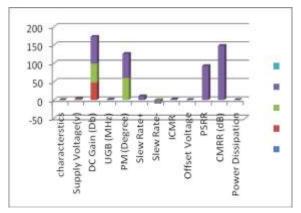

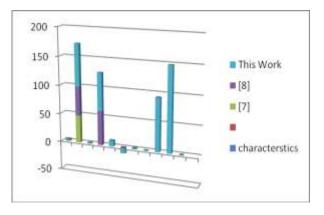

The result of the different analysis in cadence technology is listed below in tabular form. The cut off frequency at different voltages is shown in table1 and operating at supply voltage of 1.5v. Different parameter of the OP-AMP and comparison between simulated result and previous paper result had been discussed as shown in figure 2 and figure 3 were calculated at cadence technology.

Figure 2: Comparison between simulated results and previous paper

Low Power Two-Stage Operational Amplifier design using 45 nm Technology Author(s) : Navneet Dubey, Dr. Shyam Akashe | ITM University, Gwalior

Figure 3: Comparison between Previous paper and proposed work.

From the following figure 2: we had a comparisons between various simulated results of low power operational amplifiers and also for previous results which consists of supply voltage, characteristics, dc gain, UGB, PM, slew rate, ICMR (Input/output common mode range), offset voltage, PSRR (Power supply rejection ratio), CMRR (Common mode rejection ratio) along with power is being calculated with the simulated graph as shown above

|                           |             |             | 1    |                    |             | 1           |              |

|---------------------------|-------------|-------------|------|--------------------|-------------|-------------|--------------|

| Characte-<br>ristics      | [2]         | [3]         | [4]  | [5]                | [7]         | [8]         | This<br>Work |

| Supply<br>Voltage(V)      | 3           | 1.5         | 1.5  | 2                  | 1.5         | 0.8         | 1.5          |

| DCGain<br>(dB)            | 20.8<br>8   | 80          | 82   | 102                | 48          | 51          | 73.57        |

| UGB<br>(MH <sub>Z</sub> ) | 15.4        | 167         | 1.15 | 0.48               | NA          | 0.057       | 1.084        |

| PM<br>(Degree)            | -19.6       | 73.5        | 86   | 60.3<br>5          | NA          | 60          | 65.89        |

| Slew<br>Rate+             | NA          | 464         | 0.73 | 0.20               | NA          | 0.14        | 10.1         |

| Slew<br>Rate -            | NA          | NA          | 0.73 | 0.21               | NA          | NA          | -9.5         |

| ICMR                      | NA          | 1.13        | NA   | 1.13               | NA          | NA          | 1.51         |

| Offset<br>Voltage         | 50          | NA          | NA   | 0.25               | NA          | NA          | NA           |

| PSRR                      | NA          | NA          | NA   | 59.7               | NA          | NA          | 92.95        |

| CMRR<br>(dB)              | -53         | NA          | NA   | 102.<br>004        | NA          | NA          | 147.9        |

| Power<br>Dissipation      | 570<br>(μw) | 8.9<br>(mw) | NA   | 25.7<br>45<br>(mw) | 6.5<br>(mw) | 1.2<br>(µw) | 3.54<br>(µw) |

The main performance of our proposed operational amplifier are summarized in table 1; as shown the proposed operational amplifier achieve good performance characteristics in terms of DC Gain, Slew rate, and power dissipation which is as shown above.

#### **4. CONCLUSION**

This paper presents a new low power operational amplifier circuits operating with the supply voltages 1.5v and power dissipation is  $3.54(\mu w)$ . Proposed circuit can be used for wide verities of low voltages and low power application. The following paper shows simulated result having presented to demonstrate the feasibility of the proposed low power operational amplifier circuit. Cadence is used to verify the circuit performance. However in this paper we used compensation technique to minimize power consumption for maintain the circuit performance at low voltage supply reduced the threshold voltage of the transistor which impose a large number of serious problem both in circuit design and technology.

#### **5. ACKNOWLEDGEMENT**

The author would like to thank Institute of Technology and Management, Gwalior for providing the Tools and Technology for the work to be completed.

## **REFERENCES:**

- Philip E. Allen and Douglas R.Holberg, CMOS Analog Circuit Design, second edition, OXFORD UNIVERSITY PRESS, 2002

- [2] Paul R. Gray, Paul J. Hurst, Stephen H. Lewis, Robert G. Meyer, Analysis and Design of Analog Integrated Circuits, Fourth Edition, JOHN WILEY & SONS, INC, 2001.

- [3] Johan H. Huijsing, Operational Amplifiers theory and design, Kluwer Academic Publishers.

- [4] Phillip E. Allen, Benjamin J. Blolock

Low Power Two-Stage Operational Amplifier design using 45 nm Technology Author(s) : Navneet Dubey, Dr. Shyam Akashe | ITM University, Gwalior

and Grabiel A. Rincon "Low Voltage Analog circuit using standard CMOS technology"

- [5] Johan H. Huijsing, Senior Member, Ron Hogervarst and Klass-Jan de Langen "Low Power Low Voltage VLSI OPAMP cells" IEEE Transaction on circuits and systems, vol-42, No-11, p.p 841-852, Nov 95.

- [6] Eric Vittoz and Jean Fellrath "CMOS Analog Integrated Circuits Based on Weak Inversion Operation" IEEE JSSC, vol, SC-12, No-3, p.p. 224-231, June 1997.

- Johan H. Huijsing, Senior Member, Ron Hogervarst and Klass-Jan de Langen" Low Power Low Voltage VLSI OPAMP cells" IEEE Transaction on circuits and systems, vol-42, No-11, p.p 841-852, Nov95

- [8] Hervé Barthélemy, Ivane Koudobine, and Damien Van Landeghem "Bipolar Low-Power Operational Transresistance Amplifier Based on First Generation Current Conveyor" IEEE Transaction on circuits and systems —II: Analog and Digital Signal Processing, Vol. 48, No. 6, June 2001

- [9] M. Yavari and O. Shoaei "Lowvoltage low-power fast-settling CMOS operational transconductance amplifiers for switched-capacitor applications" IEEE Proc.-Circuits Devices Syst., Vol. 151, No. 6, December 2004 IJETCAS 13-335; © 2013, IJETCAS All Rights Reserved Page 174

- [10] Zushu Yan, Pui-In Mak, and Rui P. Martins "Two-Stage Operational Amplifiers: Power-and-Area-Efficient Frequency Compensation for Driving a Wide Range of Capacitive Load" Digital Object Identifier.

- [11] Manju Sandhu Manju Bala "Design of Low Voltage Low Power Operational Amplifier" IEEE DOI 10.1109/ACCT.2012.46 p.p 368-373.

- [12] M. R. Valero, S. Celma, N. Medrano, and B. Calvo, "A 0.8-V 1.2-μW railto-rail fully differential op-amp with adaptive biasing," in Proc. ESSCIR, Bordeaux, France, 2012.

- [13] Jungwon Han, Student Member, IEEE, KwisungYoo, Dongmyung Lee. Student Member, IEEE. Kangyeop Park, Student Member, IEEE, Wonseok Oh, Member, IEEE, and Sung Min Park, Member, IEEE "A Low-Power Gigabit CMOS Limiting Amplifier Using Negative Impedance Compensation and Its Application" IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 20, No. 3, March 2012

- [14] María Rodanas Valero Bernal, S. Celma, N. Medrano, Member, IEEE, and B. Calvo, Member, IEEE "An Ultralow-Power Low-Voltage Class-AB Fully Differential Operational Amplifier for Long-Life Autonomous Portable Equipment" IEEE Transaction on circuits and systems —II: Express Briefs, Vol.59, No. 10, October 2012.

- [15] Kaulberg, T. "ACMOS current-mode operational amplifier", IEEE Journal1993, Pages: 849 - 852.

- [16] Schlogl, F.; Zimmermann, H. "Low-voltage operational amplifier in 0.12μm digital CMOS technology"

IET Journal 2004, Pages: 395 398.

- [17] Schlogl, F.; Dietrich H.;

Zimmermann, H."High-gain highspeed operational amplifier in digital 120nm CMOS", IEEE Conference 2004, Pages: 316 - 319.

- [18] Sarbishaei, H.; Kahookar Toosi, T.;

Low Power Two-Stage Operational Amplifier design using 45 nm Technology Author(s) : Navneet Dubey, Dr. Shyam Akashe / ITM University, Gwalior

Zhian Tabasy, E.; Lotfi, R. "A highgain high- speed low-power class AB operational amplifier", IEEE Conference 2005, Pages: 271- 274 Vol. 1

- [19] Hiyuan Li; Jianguo Ma; MingyanYu; Yizheng Y Low noise operational amplifier design with current driving bulk in 0.25µm CMOS technology", IEEE Conference 2005, Pages: 630 -634

- [20] Linear integrated circuit author name:

-D. Roy Chaudhary and Shailb Jain revised second edition and publication year 2003/2005, pages:99-100.