Volume 5 Issue 1 | March 2017

ISSN: 2320-9984 (Online)

# International Journal of Modern Engineering & Management Research

Website: www.ijmemr.org

### **Analysis of AES Algorithm Using S-BOX**

### **Ankit Soni**

M. Tech. Research Scholar

Vindhya Institute of Technology And Science

Jabalpur (M.P.), [INDIA]

Email: ankitsoni.ec@gmail.com

Abstract—In this paper essential investigation of AES calculation with the non serviceable perspectives i.e.hoisted execution, high throughput, and range effectiveness is advertised. This paper will show the hypothetical investigation parameter varieties in the era of the S-BOX. The Rijndael figure, planned by Joan Daemen and Vincent Rijmen, is specific as approved Advance Encryption standard (AES) and it is well-suited for equipment work out.

**Keywords:**—AES, DES, 3DES, Cryptography, S-Box, Multi-encryption.

### 1. INTRODUCTION

To keep up information secure, mystery and copyright shielded from grouped programmers and unapproved induction and clients, various strategies have been developed, for example, cryptography, steganography. Cryptography is essential backbone in the realm of systems administration; ordinarily use in equipped and observation purposes. Cryptography gives the vital component to give privacy, responsibility and precision in system correspondence and other related fields.

Propelled Encryption Standard (AES) was issued as Federal Information Processing Standards by national establishment (FIPS) by National Institute of Standards and innovation (NIST). This paper utilizes 128 piece key created by key booking calculation.

### **Amit Mishra**

Assistant Professor

Department of Electronics & Communication Engg.

Vindhya Institute of Technology And Science

Jabalpur (M.P.), [INDIA]

Email: amit\_2440@yahoo.co.in

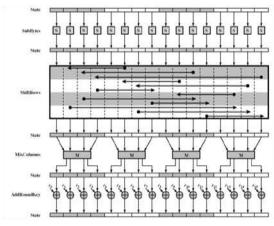

Examination of Rijndael Algorithm goes through the 4 layers comprises of

- i. ByteSub Transformation (S-Box Creation),

- ii. ShiftRow Transformation,

- iii. MixColumn Transformation,

- iv. AddRound Key

This paper concentrate on point by point study about the non linearity of the S-Box which is a critical segment of AES, which utilizes procedure of relative mapping and Invfor encryption relative mapping unscrambling separately for lifted execution, high throughput and zone effectiveness. AES design displayed utilizes Polynomial increase utilizing XOR changes as a substitute of multipliers to decrease the equipment unpredictability. In the proposed engineering both encryption and unscrambling rounds are performed on a similar equipment assets, correspondingly assembling plan territory productive. A look into table is figured utilizing Verilog equipment portrayal dialect. A proper utilization of look into table in S-Box creation can be extremely powerful in examination of AES calculation. S-Box is critical segment layer in the investigation prompting security of figure as it relies on upon the nonlinearity consider. [3] [6] [9] since the symmetric figure drives speedier than topsy -turvy figure so they are predominant in a similar field. S-box is the main component that infuses the nonlinearity in the figure making it all the more effective. The accompanying table demonstrates the no of keys as indicated by the piece estimate. [8][2].

### 1.1 Rijndael Algorithm

Rijndael (articulated rain-dahl) is the calculation that has been chosen by the U.S. National Institute of Standards and Technology (NIST) as the possibility for the Advanced Encryption Standard (AES). It was chosen from a rundown of five finalists, that were themselves chosen from a unique rundown of more than 15 entries. Rijndael will start to supplant the Data Encryption Standard (DES) and later Triple DES - throughout the following couple of years in numerous cryptography applications. The calculation was outlined by two Belgian cryptologists, Vincent Rijmen and Joan Daemen, whose surnames are reflected in the figure's name. Rijndael has its starting points in Square, a prior cooperation between the two cryptologists.

The Rijndael calculation is another era symmetric square figure that backings key sizes of 128, 192 and 256 bits, with information taken care of in 128-piece pieces - notwithstanding, in overabundance of AES outline criteria, the square sizes can reflect those of the keys. Rijndael utilizes a variable number of rounds, contingent upon key/square sizes, as takes after:

- 9 rounds if the key/piece size is 128 bits

- 11 rounds if the key/square size is 192 bits

- 13 rounds if the key/piece size is 256 bits

Rijndael is a substitution straight change figure, not requiring a Feistel arrange. It utilize triple prudent invertible uniform changes (layers). In particular, these are: Linear Mix Transform; Non-direct Transform and Key Addition Transform. Indeed, even before the first cycle, a straightforward key option layer is performed, which adds to security. From that

point, there are Nr-1 adjusts and after that the last round. The changes shape a State when begun yet before consummation of the whole procedure.

The State can be considered as an exhibit, organized with 4 lines and the section number being the piece length isolated by bit length (for instance, separated by 32). The figure key comparably is an exhibit with 4 lines, yet the key length separated by 32 to give the quantity of sections. The pieces can be deciphered as unidimensional varieties of 4-byte vectors.

Figure 1. Components oF S-Box

### 2. AES BLOCKS DETAILS

Cryptographic technology is a necessary way to make sure information security, and is the key to data safety. In all kinds of cryptographic algorithms, Advanced Encryption Standard Algorithm (AES) is highly preferred as it offers very high security, flexibility, efficiency, convenient usage, and good performance [4].

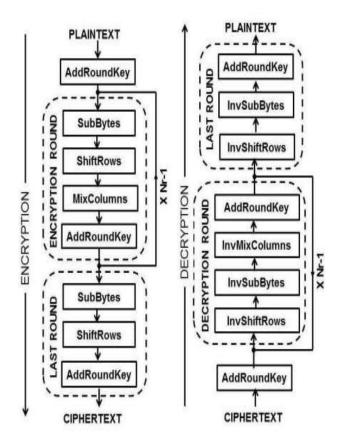

# State AddRoundKey Initial round 1-SubBytes 2-ShiftRows 3-MixColumns 4-AddRoundKey Round key 0 rounds SubBytes ShiftRows AddRoundKey AddRoundKey Flound key 10 Final round

Figure 2. AES Blocks

### 2.1 The AES Approach

The AES calculation is a symmetric Key piece encryption that can figure, and unravel, (decode), data. Encryption changes over information to a confused (bewildered) shape called Ciphered-content. Decoding of the figured content recovers the information once again into its unique shape, which is called plaintext (i.e. unique information). The AES calculation can utilize cryptographic keys of 128, 192 and 256 bits to encode and decode information in the squares of bits [7]. AES encryption is indicated as various reiterations of change adjusts that change over the information plaintext into the last yield of figured content [5].

Each round comprises of various preparing steps, including one that relies on upon the figure key. An arrangement of switch rounds are connected to AES utilize outline standard known as a Substitution change organize [5]. Despite the fact that its antecedent, DES does not utilize a Feistel arrange. AES works on a 4x4 exhibit of bytes called state which is a grid frame. The calculation comprises of performing four detached basic operations. These operations names as: Sub Bytes, Shift Rows, Mix Columns and Add Round Key [5].

AES works on a 4x4 exhibit of bytes ("state"). The strategy comprises of performing 4 unique operations [5].

### 2.1.1 SubBytes Transformation:

Subbytes Transformation is a non-linear byte substitution that operates independently on each byte (8 bit) of the state using a substitution table (S-box) <sup>[5]</sup>. AES use 8 bit input and 8 bit output for Substitution box.

Table 2.1 The S-Box-8

|    |     | ¥  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |

|----|-----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|

|    | - [ | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | a  | ь  | c  | d  | e  |   |

| 1  | 0   | 63 | 7c | 77 | 7b | £2 | 6b | 6f | c5 | 30 | 01 | 67 | 2b | fe | d7 | ab | 7 |

|    | 1   | ca | 82 | c9 | 7d | fa | 59 | 47 | f0 | ad | d4 | a2 | af | 9c | a4 | 72 | C |

| Ú  | 2   | b7 | fd | 93 | 26 | 36 | 3f | f7 | cc | 34 | a5 | e5 | f1 | 71 | d8 | 31 | 1 |

|    | 3   | 04 | c7 | 23 | c3 | 18 | 96 | 05 | 9a | 07 | 12 | 80 | e2 | eb | 27 | b2 | 7 |

|    | 4   | 09 | 83 | 2c | 1a | 1b | 6e | 5a | a0 | 52 | 3b | d6 | ь3 | 29 | e3 | 2f | 8 |

| 9  | 5   | 53 | d1 | 00 | ed | 20 | fc | b1 | 5b | 6a | cb | be | 39 | 4a | 4c | 58 | c |

| ij | 6   | d0 | ef | aa | fb | 43 | 4d | 33 | 85 | 45 | f9 | 02 | 7f | 50 | 3с | 9f | a |

|    | 7   | 51 | a3 | 40 | 8f | 92 | 9d | 38 | f5 | bc | b6 | da | 21 | 10 | ff | f3 | d |

| x  | 8   | cd | 00 | 13 | ec | 5f | 97 | 44 | 17 | 04 | a7 | 7e | 3d | 64 | 5d | 19 | 7 |

| ij | 9   | 60 | 81 | 4f | do | 22 | 2a | 90 | 88 | 46 | ee | P8 | 14 | de | 5e | 0Ъ | d |

| ì  | a   | e0 | 32 | 3a | 0a | 49 | 06 | 24 | 5c | c2 | d3 | ac | 62 | 91 | 95 | e4 | 7 |

| ř  | Ъ   | e7 | c8 | 37 | 6d | 8d | d5 | 4e | a9 | 6c | 56 | f4 | ea | 65 | 7a | ae | 0 |

| i  | С   | ba | 78 | 25 | 2e | 10 | a6 | b4 | c6 | e8 | dd | 74 | 1f | 4b | bd | 8p | 8 |

|    | d   | 70 | 3e | b5 | 66 | 48 | 03 | f6 | 0e | 61 | 35 | 57 | Ъ9 | 86 | c1 | 1d | 9 |

| Ü  | e   | e1 | f8 | 98 | 11 | 69 | d9 | 8e | 94 | 9b | 1e | 87 | e9 | ce | 55 | 28 | d |

| n  | f   | 8c | ai | 89 | 0d | bf | e6 | 42 | 68 | 41 | 99 | 2d | Of | ъ0 | 54 | bb | 1 |

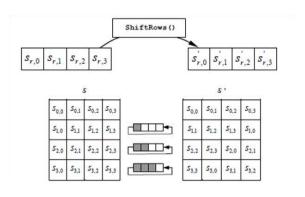

### 2.1.2 ShiftRows Transformation:

The first row, r = 0, is not shifted. The shift value

shift (r, Nb) depends on the row number, r, as follows (recall that Nb = 4)<sup>[7]</sup>:

$$shift(1,4) = 1$$

;  $shift(2,4) = 2$ ;  $shift(3,4) = 3$

ShiftRows ( ) cyclically shifts the last three rows in the state.

Figure 2.2 Shift-Rows Transformation

### 2.1.3 Shift Rows Transformation:

The Mix-Columns () change works on the State section by-segment, regarding every segment as a four-term polynomial [5]. In the MixColumns step, every segment of the state is duplicated with a settled polynomial a(x). In the MixColumns step, the four bytes of every segment of the state are consolidated utilizing an invertible direct change [5]. The MixColumns work takes four bytes as info and yields four bytes, where each information byte influences every one of the four yield bytes [5].Columns are considered with fixed

$$a(x) = 3x^3 + 1x^2 + 1x + 2...$$

(1)

Polynomial a(x), given by

$$\begin{bmatrix} s_{0,c} \\ s_{1,c} \\ s_{2,c} \\ s_{3,c} \end{bmatrix} = \begin{bmatrix} 02 & 03 & 01 & 01 \\ 01 & 02 & 03 & 01 \\ 01 & 01 & 02 & 03 \\ 03 & 01 & 01 & 02 \end{bmatrix} \begin{bmatrix} s_{0,c} \\ s_{1,c} \\ s_{2,c} \\ s_{3,c} \end{bmatrix}$$

Let

$$s'(x) = a(x) \otimes s(x)$$

: .....(2)

For 0 = c < Nb MixColumns ( ) operates on the state column-by-column.

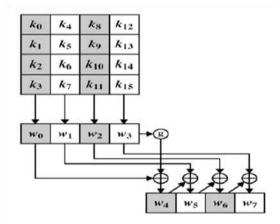

### 2.1.4 Add Round Key Transformation:

A Round Key is added to the yield of MixColumn operation (state) by a straightforward bitwise XOR operation. For each round of operation, separate key is produced utilizing Key Expansion [5].

The AES key development calculation takes as information a 4-word key and creates a direct exhibit of 44 words. Each round utilizations 4 of these words. Each word contains 32 bytes which implies each subkey is 128 bits in length [5]. The key is replicated into the initial four expressions of the extended key. The rest of the extended key is filled in four words at any given moment. Each additional word w[i] relies on upon the promptly going before word, w[i-1], and the word four positions back w[i-4]. In three out of four cases, a straightforward XOR is utilized [5]. For a word whose position in the w exhibit is a various of 4, a more intricate capacity is utilized. Figure 5.3 outlines the era of the initial eight expressions of the extended key utilizing the image g to speak to that perplexing capacity [5].

The capacity g comprises of the accompanying sub functions:

- 1. RotWord plays out a one-byte roundabout left move on a word. This implies an info word [b0, b1, b2, b3] is changed into [b1, b2, b3, b0] [5].

- 2. SubWord plays out a byte substitution on every byte of its info word, utilizing the s-box portrayed prior [5].

- 3. The consequence of steps 1 and 2 is XORed with round consistent, Rcon[i]. The round consistent is a word in which the three furthest right bytes are dependably 0. Therefore the impact of a XOR of a word with Rcon is to just play out a XOR on the furthest left byte of the word. The round steady is diverse for each round and is characterized as Rcon[j] = (RC[J],0,0,0), with RC[1]=1, RC[j]=2RC[j -1] and with increase characterized over the field GF(28) [5].

The key extension was intended to be impervious to known cryptanalytic assaults. The consideration of a round-ward round consistent disposes of the symmetry, or closeness, between the route in which round keys are produced in various rounds [5].

Figure 2.3: The Key Expansion-I

Figure 2.4: The Key Expansion-II

The ShiftRows column is depicted here as a linear shift which gives a better idea how this section helps in the encryption <sup>[5]</sup>.

## 3. AES ALGORITHM WITH VARIOUS SECURITY APPLICATIONS

Iman Saberi et.al.,[3] paper examines a new strategy in AES-256 Key Expansion. This strategy is separated into two sections. Initial segment is Key Extension which creates 64 words from eight figure catchphrases. Second part is E-O Select Round Key that chooses the 60 words from 64 created words in Key Expansion, utilizing particular calculation which depends on seven levels, odd and even position of each word. To total up, fourteen round keys and one pre round key are being created. This strategy enhances multifaceted nature of E-O strategy as opposed to exemplary strategy.

E. J. Swankoski et.al, [4] recommended a parallel design in which inside equipment usefulness is reused. This is the place circle unrolled designs utilize copied equipment. Sensibly minimized single square made by equipment that is perfect duplication. This makes greater security, accomplished by the physical partition of individual encryption units. It considers a higher level of versatility, and throughput of the framework ends up plainly diminished just by accessible physical assets and accessibility of the input-yield measure. The parallel encryption plot licenses for tantamount execution contrasted with typical pipelined

models with more noteworthy adaptability what's more, equipment productivity.

Anurhea Dutta et.al.,[5] built up the idea of an enhanced crossover AES-DES as the methods for reinforcing the current AES engineering.

This calculation is more secure and assault safe encryption calculation which can be utilized as a part of different ranges like electronic monetary exchanges, satellite interchanges, shrewd cards, protection part, and remote interchanges. The name "Crossover" implies that this encryption calculation has worked in components which have been gotten from both of the constituent guidelines. The security is made enhanced by expanding the emphasess.

Tianshan Chen et.al.,[6] introduced two highperformance executions of Ghash center. In light of the altered piece parallel strategy, 4arrange pipelines are misused with the end goal of higher execution. To take care of the enormous fan-out issue gotten from bit-parallel multiplier, this paper presents excess enlist strategy. The exploratory outcomes demonstrate that excess registers productively diminish routig delay in FPGA. Two design examples are evaluated on target FPGA Xilinx Virtex-4LX60-ff668-11. The throughput of Ghash\_f can easily reach to 312.5MHZ\*128bit=40Gbps, which is the fastest Ghash implementation on FPGA to date. Qiang Liu et.al.,[9] demonstrated a design which achieves a throughput of 75.9 Gbps using a single pipeline on a latest FPGA device. Two parallel implementations of the suggested design can meet the real-time encryption/decryption demand for 100 Gbps data rate. A new key expansion scheme is proposed to address the issues of existing key expansion scheme used in AES. The new scheme increased the complexity of key cracking and the speed of AES. Sharanagouda N Pati et.al.,[10] proposed a design is implemented based on the iterative approach for cryptographic algorithms. The major applications of SDRs are Blue- tooth, WLAN, GPRS. WCDMA Radar, etc. being

2015.

implemented using SDR technology. A Software Defined Radio can be defined as a radio in which some physical layer functions or all of the physical layer functions are software defined. The higher levels of HDLs are used to define encryption/decryption functions of the system. Today software defined technology offers many advantages such as enhancements without affecting the radio hardware, terminals that can cope with the unpredictable dynamic features of highly variable wireless links, accurate use of radio spectrum and power, and many others.

### 4. CONCLUSION

In this paper AES algorithm with various security applications are surveyed. In AES-256 Key expansion method is divided into two parts, one is key expansion and other is E-O select round key. It is based on evenodd position. So the complexity of algorithm is improved than normal AES. In other method loop-unrolled architectures use duplicated hardware. Reasonably compact single block created by reused hardware that is ideal for duplication. This method is increased more security than conventional method. In other method, hybrid AES-DES strengthening the algorithm and resist the attacks in this algorithm. The Gash core method increases the speed of algorithm by using FPGA platform. The suggested scheme is faster than the existing method with 75.9 Gbps and increases the complexity of cracking keys by using enhanced key expansion block. This secured AES can be used in various security related fields such as wireless communication, satellite communication, defense sector etc

### **REFERENCES:**

- [1] William Stallings "Network Security Essentials (Applications and Standards)", Pearson Education, 2004.

- [2] Nivedita Bisht and Sapna Singh "A Comparative Study of Some Symmetric and Asymmetric Key Cryptography Algorithms", IJIRSET,

- [3] Iman Saberi, Bahareh Shojaie and Mazleena Salleh, "Enhanced Key Expansion for AES-256 by Using Even Odd Method", IEEE, 2010.

- [4] E. J. Swankoski, R. R. Brooks, V. Narayanan, M. Kandemir, and M. J. Irwin, "A parallel architecture for secure FPGA symmetric encryption" in Proc. 18th Int. Parallel Distrib. Process. Symp., Santa Fe, NM, Apr. 2004, p. 132.

- [5] Anurhea Dutta, Prerna Bharti, Swati Agrawal, Surekha K S, "Hybrid AES-DES Block Cipher: Implementation using Xilinx ISE9.1i", UACEE International Journal of Advancements in Electronics and Electrical Engineering, 2010.

- [6] Tianshan Chen, Wenjie Huo, Zhenglin Liu, "Design and Efficient FPGA Implementation of Ghash Core for AESGCM", IEEE, 2010.

- [7] Vasamsetti Ramoji, "Highly Secured High Throughput Efficient VLSI Architecture for AES Implementations", IJRCCT, 2012.

- [8] M. Vanitha, R. Sakthivel; Subha "Highly secured high throughput VLSI architecture for AES algorithm" Devices, Circuits and Systems (ICDCS), International Conference, 2012.

- [9] Qiang Liu, Zhenyu Xu, and Ye Yuan, "High throughput and secure advanced encryption standard on FPGA with fine pipelining and enhanced key expansion", IET, 2014.

- [10] Sharanagouda N Patil and R.M.Vani, "Data Security Using Advanced Encryption Standard (AES) In Reconfigurable Hardware For SDR Based Wireless Systems", IJCET,

2015.

- [11] Manjesh. K. N, R K Karunavath, "Secured High throughput implementation of AES Algorithm", IJARCSSE, 2013.

- [12] Hrushikesh S. Deshpande, Kailash J. Karande, Altaaf O. Mulani, "Efficient Implementation of AES Algorithm on FPGA" Progress In Science in Engineering Research Journal, 2014.

- [13] Prof. S. Venkateswarlu, Deepa G.M, and G. Sriteja, "Implementation of Cryptographic Algorithm on FPGA", IJCSMC, 2013.

- [14] Yi Wang and Yajun Ha "FPGA-Based 40.9-Gbits/s Masked AES with Area Optimization for Storage Area Network", IEEE, 2013.

- [15] Qiang Liu, Zhenyu Xu, and Ye Yuan "A 66.1 Gbps Single pipeline AES on FPGA", IEEE, 2013.